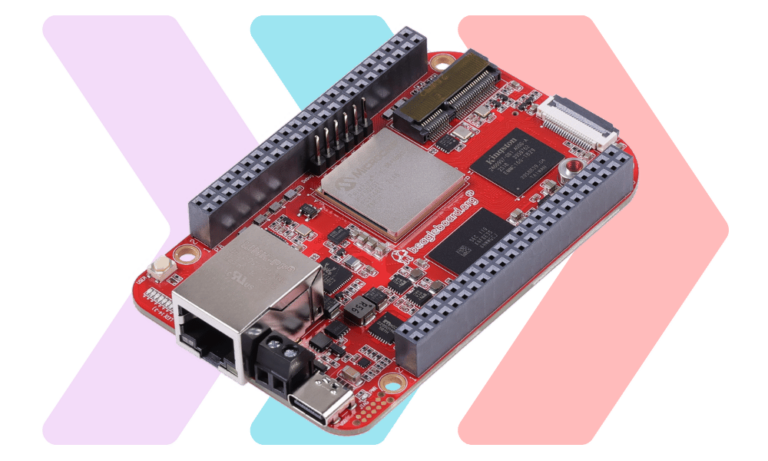

The BeagleV-Fire just got faster. The BeagleV-Fire gateware repo now fully supports Microchip’s SmartHLS compiler, opening the door for developers to create custom FPGA accelerators directly from C/C++ code — no HDL expertise required.

SmartHLS (High-Level Synthesis) revolutionizes FPGA development by allowing software engineers to describe hardware behavior in familiar languages like C and C++, while the toolchain automatically generates optimized Verilog for hardware implementation. The BeagleV-Fire gateware flow integrates SmartHLS accelerators seamlessly with the RISC-V subsystem via AXI4 interfaces, automatically handling memory mapping, DMA setup, and device tree configuration.

A great example is the new sine calculation accelerator, which demonstrates a remarkable 10× performance gain (1022.79% faster) over a standard cmath implementation — all built from just a few lines of C++!

Try it yourself with a single command:

python3 build-bitstream.py ./build-options/sin-shls-apu.yaml

To help you get started, Microchip SmartHLS team has published a growing collection of SmartHLS example projects and library components:

With this integration, BeagleV-Fire becomes an accessible platform for software developers, educators, and researchers to harness FPGA acceleration — combining the flexibility of C/C++ with the performance of custom hardware.

Start coding, compiling, and accelerating — the future of fast FPGA development is here with SmartHLS on BeagleV-Fire.